|

Страница 12 из 14

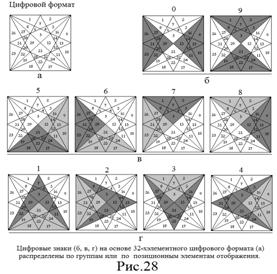

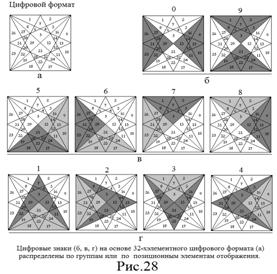

При этом три разряда (Х1, Х2, Х3) двоичного кода (рис.23) используются для построения структурной схемы преобразователя двоичного кода в 32-хпозиционный код, как при формировании 8 цифровых знаков от 0 до 7 (рис.24), так и при формировании 8 цифровых знаков от 8 до 15 (рис.25). Четвертый разряд (Х4) двоичного кода используется в качестве разрешающего сигнала  (Q1) с уровнем логической единицы «1» на формирование цифровых знаков от 0 до 7 (рис.24) и разрешающего сигнала Х4 (Q2) с уровнем логической единицы «1» на формирование цифровых знаков от 8 до 15 (рис.25). (Q1) с уровнем логической единицы «1» на формирование цифровых знаков от 0 до 7 (рис.24) и разрешающего сигнала Х4 (Q2) с уровнем логической единицы «1» на формирование цифровых знаков от 8 до 15 (рис.25).

При формировании, например, 128 цифровых знаков, построение структурной схемы преобразователя двоичного кода в 32-хпозиционный код должно быть распределено на 16 этапов (I - XVI) этапов, по числу распределения цифровых знаков на группы I-XVI (рис.26).

Прежде всего, построим предварительно структурную схему преобразователя двоичного кода в 32-хпозиционный код, используя 8 этапов (I-VIII) ее построения, при формировании цифровых знаков от 0 до 63 (рис. 26), распределив их на 8 групп (I-VIII). Для восьми структурных схем преобразователей двоичного кода в 32-хпозиционный код (I-VIII), используя три разряда (Х1, Х2, Х3) двоичного кода (рис.23), при формировании 8 цифровых знаков, потребуется схема управления (рис.27в), распределяющая сигналы разрешения на формирование той или иной группы (I-VIII) цифровых знаков (рис.26).

В схеме управления используются разряды Х4, Х5, Х6 двоичного кода. При подаче разрешающего сигнала  (используется инверсный разряд (используется инверсный разряд  двоичного кода) с уровнем логической единицы «1» в схеме управления (рис.27в) последовательно формируются разрешающие сигналы (Q1-Q8) на формирование 8 групп (I-VIII) цифровых знаков. Формирование первых двух групп (I и II) цифровых знаков (0-7) и (8-15) осуществляется с использованием структурных схем преобразователей кода (I и II) показано на рис. 24 и рис.25, соответственно. двоичного кода) с уровнем логической единицы «1» в схеме управления (рис.27в) последовательно формируются разрешающие сигналы (Q1-Q8) на формирование 8 групп (I-VIII) цифровых знаков. Формирование первых двух групп (I и II) цифровых знаков (0-7) и (8-15) осуществляется с использованием структурных схем преобразователей кода (I и II) показано на рис. 24 и рис.25, соответственно.

Для остальных 6 групп (III-VIII) цифровых знаков (16-23, 24-31, 32-39, 40-47, 48-55, и 56-63) построение структурных схем преобразователей двоичного кода в 32-хпозиционный код происходит аналогично рис.24 и рис.25. Структурные схемы преобразователей кода будут только отличаться как различием начертания формируемых знаков, так и соответствующим им разрешающим сигналом управления (Q3-Q8).

Построение структурной схемы преобразователя двоичного кода в 32-хпозиционный код при формировании цифровых знаков от 64 до 127 (IX-XVI) происходит аналогично. При подаче разрешающего сигнала Х7 (используется прямой разряд двоичного кода) с уровнем логической единицы «1» в схеме управления (рис.27г) последовательно формируются разрешающие сигналы (Q9-Q16) на формирование 8 групп (IX-XVI) цифровых знаков. Все 16 структурных схем преобразователей двоичного кода в 32-хпозиционный код объединены разделяющими диодами (аналогично рис.24, рис.25), позволяя сформировать на одном формате индикатора 128 фигур, представленных тем или иным цифровым знаком.

|